※ 전자책 업데이트 공지: 아래 정오사항이 반영된 ver3.0이 2023년 10월 4일 업데이트 됐습니다.

# 2022년 10월 10일 5쇄본 정오표 #

* 이전 1~4쇄를 구입하신 독자분들도 확인하시기 바랍니다 # 전자책 ver 2.0 오류 사항

p71. 본문 마지막 줄 (영문 병기 오타)

nomalization → normalization

p79. 표 1-11 아스키 코드표

10진수 80 16진수 5 → 10진수 80 16진수 50

p86. 본문 7~10째줄

주(primary) 색, 주 색 → 원색

p86. 그림 1-18 오른쪽 상단

청록색(시안) → 청록색(사이언)

p87. 본문 2째 줄

주 색 → 원색

p92. 각주 2째 줄

(log(0)=1이라서 그렇다) → (log(1)=0이라서 그렇다)

p108. 각주 3째 줄

전기가 전원에서 나와 → 전류가 전원에서 나와

p113. 본문 10째 줄

진공 튜브도 → 진공관도

p114. 본문 7째 줄

필드 효과 트랜지스터(FET, field effect transistor) → 전계 효과 트랜지스터(FET, field effect transistor)

p118. 본문 밑에서 2째 줄

출력이 0이면 오른쪽 곡선을 사용하고, 출력이 1이면 왼쪽 곡선을 사용한다.

→

출력이 0이면 왼쪽 곡선을 사용하고, 출력이 1이면 오른쪽 곡선을 사용한다.

p122. 본문 10~11째 줄

PLH는 0(하이high)에서 1(로우low)로 갈 경우

→

PLH는 0(로우low)에서 1(하이high)로 갈 경우

p139. 본문 8~9째 줄

p139. 각주

p166. 본문 15~16째 줄 / 옮긴이 주석부 // p.167 그림 4-2, 첫 번째 줄, 5째 줄

긴 워드 → 롱 워드

p176. 본문 밑에서 4째 줄 (영문 병기 위치 변경)

3주소 명령어(three-address)가 → 3주소(three-address) 명령어가

p183. 표 4-4의 3행 // [0010 주소] 행 설명부 (오타)

누신기에 1을 → 누산기에 1을

p185. 그림 4-22 프로그램 카운터의 세 번째 입력

Id/cnt (대문자 I) → ld/cnt (소문자 l)

p201. 본문 위에서 13째 줄(영문 병기 오타)

'나중에 들어온 것이 먼저 나간다(last in, firt out)' → '나중에 들어온 것이 먼저 나간다(last in, first out)'

p208. 그림 5-10 아래 본문 4째 줄

(이진수로는 110100) → (이진수로는 1100100)

p231. 그림 6-13 아래 본문 4째 줄

000, 001, 011, 010, 110, 111, 101, 110 → 000, 001, 011, 010, 110, 111, 101, 100

p242. 본문 11째 줄(원서 정오표 수정사항)

멧칼프의 발명에서 큰 혁신은 바로 랜덤 백오프 후 재시도(random back-off-and-retry)다.

→

멧칼프는 랜덤 백오프 후 재시도(random back-off-and-retry)를 사용했는데, 미국 하와이 대학에서 개발한 패킷 스위치 네트워크인 알로하넷(ALOHAnet)에 이 혁신이 처음 도입됐다.

p267. 그림 6-53 디스플레이 목록

3. (7, 5)로 이동 --> (8, 5)으로 이동

4. (7, 0)으로 이동 --> (8, 0)으로 이동

8. (7, 5)로 이동 --> (8, 5)로 이동

10. (5, 3)까지 선 그림 --> (6, 3)까지 선 그림

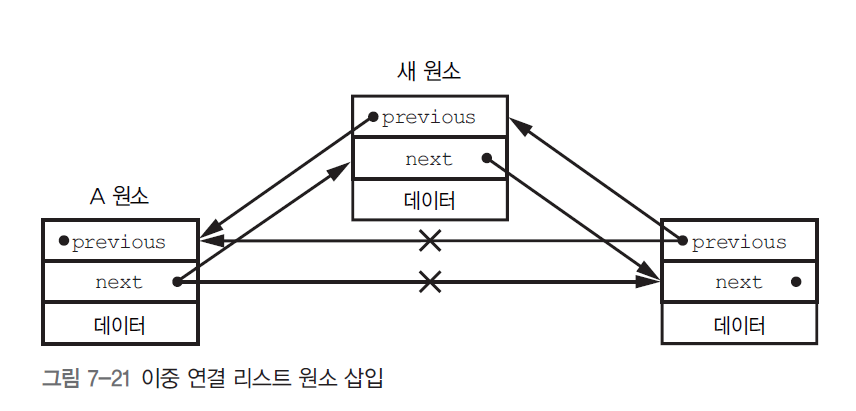

p294. 그림 7-21

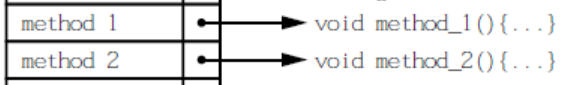

p311. 그림 7-39 메서드 (오른쪽 코드 일부 수정)

p312. <정렬> 섹션 첫째 줄

가나나순 → 가나다순

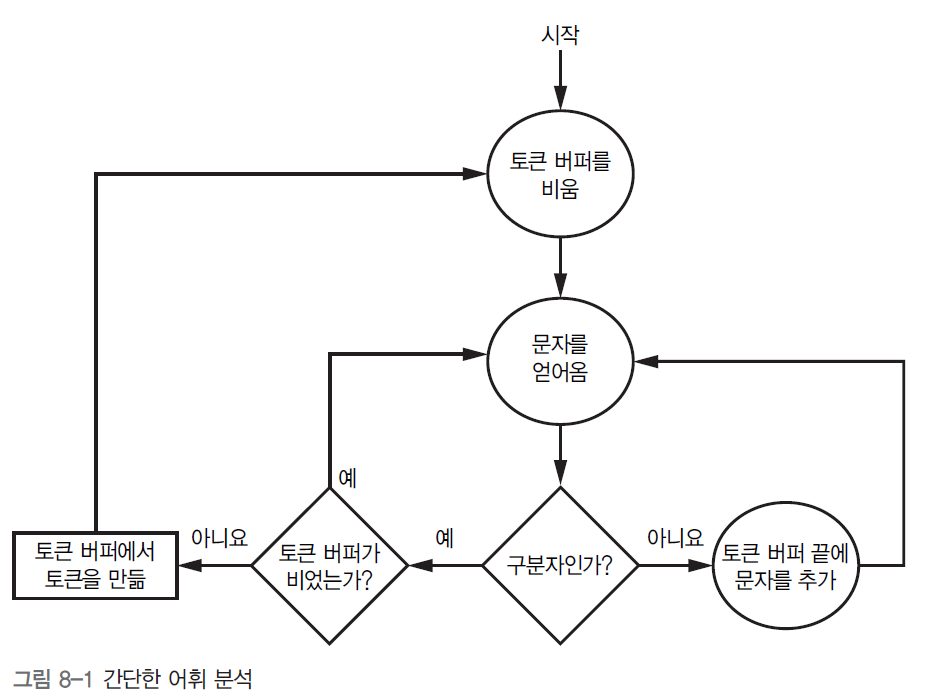

p324. 그림 8-1

p334. 본문 밑에서 5째 줄

가상 머신는 → 가상 머신은

p343. 리스트 8-13 제목 / 본문 6째 줄

감도 절감을 거친 C 루프 코드 → 강도 절감을 거친 C 루프 코드

감도 절감 시 → 강도 절감 시

p353. 표 9-1 트리 관련 용어 中 7째 의미

자식의 자식 등의 관계가 있는 노드 → 자식의 자식의 자식 등의 관계가 있는 노드

p356. 표 9-2 CSS 실렉터 中 7째 패턴

E - F → E ~ F

p361. 본문 밑에서 6째 줄 영어 병기

Xtensible Stylesheet Language Transformations → eXtensible Stylesheet Language Transformations

p381. 리스트 10-4 中 밑에서 3째 줄 (코드 안 따옴표 삭제)

("<div>'그럴 줄 알았습니다!</div><p>"); → ("<div>그럴 줄 알았습니다!</div><p>");

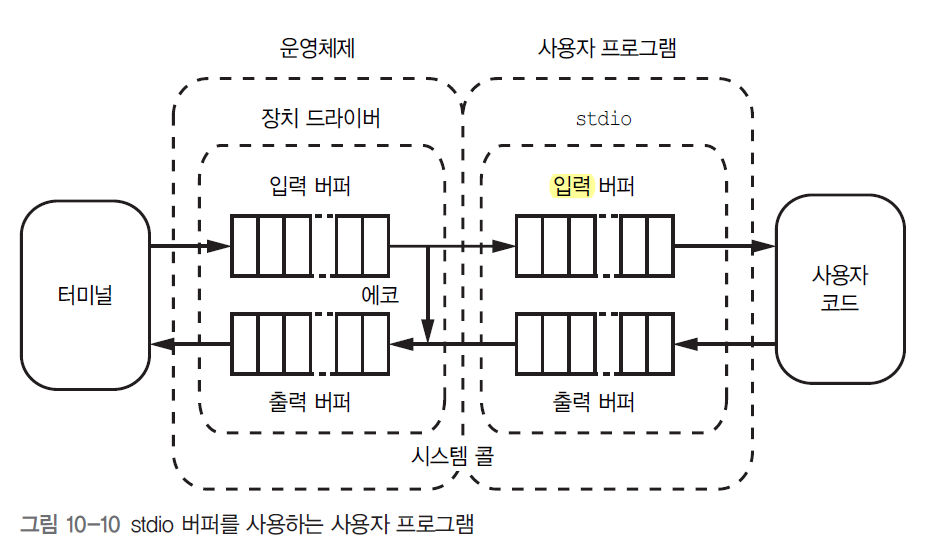

p388. 그림 10-10 中 사용자 프로그램

p398. 134행 코드 中 (주석 삭제)

(void)printf( // 한글 번역 생략

p415. 본문 6째 줄 / 12째 줄

13번째 줄 → 18번째 줄 / 14번째 줄 → 19번째 줄 // 19번째 줄 → 24번째 줄

p425. 본문 8째 줄

dx는 항상 양수이지만 → dh는 항상 양수이지만

p443. 본문 6째 줄 / 마지막 줄

25.565°→ 26.565°

코사인을 얻으려면 탄젠트를 얻으려면

p445. 본문 밑에서 2째 줄

57.529°의 사인값 및 코사인값과 → 57.529°의 코사인값 및 사인값과

p478. 코드 맨 아랫 줄

// 앨범 식별를 서버에 보내고 앨범 표지 이미지의 URL을 돌려받는다.

→

// 앨범 식별자를 서버에 보내고 앨범 표지 이미지의 URL을 돌려받는다.

p479. 코드 첫째 줄

// document에 image 엘리먼트를 추가해서 앨범 표지를 표시한다.

→

// document에 img 엘리먼트를 추가해서 앨범 표지를 표시한다.

p493. 본문 13째 줄 (영어 병기 수정)

스테퍼 모터(stepper moter) → 스테퍼 모터(stepper motor)

p503. 본문 7째 줄

왼쪽에는 숨겨져 있는 메시지가 있다. → 오른쪽에는 숨겨져 있는 메시지가 있다.

p504. 본문 15째 줄

정보의 자유 법안(Freedom of Information)에 대한 → 정보 자유법(Freedom of Information)에 따라

p511. 본문 밑에서 7째 줄

클렙토그래픽 → 클렙토그래피

p540. 본문 6째 줄

베이스 정리(Bayes’ theorem)를 → 베이즈 정리(Bayes’ theorem)를

p546. 그림 14-9

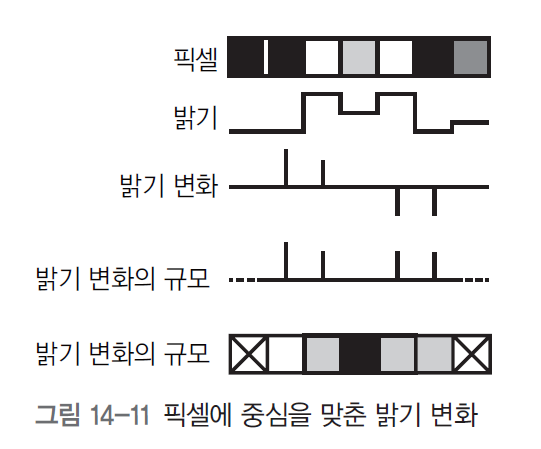

p547. 그림 14-11

p598. 본문 8째 줄

“create에 e를 추가하고 싶어요.” → “creat에 e를 추가하고 싶어요.”

# 2022년 1월 14일 4쇄본 정오표 #

* 이전 1, 2, 3쇄를 구입하신 독자분들도 확인하시기 바랍니다 (전자책 ver2.0에는 모두 수정/반영된 사항입니다)

p125. 첫 줄

오픈 컬렉터 입력이 1이면 → 오픈 컬렉터 출력이 1이면

p378. 리스트 10-2 14행새로은 동물 이름을 얻는 대화 → 새로운 동물 이름을 얻는 대화

p383. 동물 추측 게임 버전 2: C 프로그램 절 첫 줄

고수준 가상 머신다 → 고수준 가상 머신이다

# 2021년 8월 20일 3쇄본 정오표 #

* 초판 1쇄와 2쇄를 구입하신 독자분들도 확인하시기 바랍니다 (전자책 ver2.0에는 모두 수정/반영된 사항입니다)

p67. 표 1-6 [비트 개수] 12의 [값의 범위] 시작 숫자 오류(음의 부호 누락)

-2,048 ... 2,047

p83. "문자를 사용한 수 표현" 절의 본문 첫 줄

문자(예: A)를 표현하는 비트들(2진수 0000000001000000)로부터 나온 숫자들(0x0041) ...

→ ... (2진수 0000000001000001)로부터 나온 숫자들(0x0041) ...

p101. 본문 2-3째줄 ※ 오역은 아니지만, 독자의 이해를 돕기 위해 수정합니다.

하지만 앞에서 본 것처럼, 숫자 하나보다는 10비트를 사용하는 편이 훨씬 더 좋다.

→ 하지만 앞서 손가락 예제에서살펴본 것처럼, 10진 숫자 하나보다는 10비트를 사용하는 편이 훨씬 더 좋다.

p125. 본문 6째줄 ※ 오역은 아니지만, 독자의 이해를 돕기 위해 수정합니다.

한편 오픈 컬렉터 출력값 중 출력이 0인 값이 있다면

→ 한편 오픈 컬렉터 출력값 중 0인 값이 있다면

p390. 그림 10-14 아래 첫 줄 (오타 수정)

그림을 보면 out 화살표가 시계 방향으로 out 화살표를 따라잡기 전까지는

→ 그림을 보면 in 화살표가 시계 방향으로 out 화살표를 따라잡기 전까지는

# 2021년 5월 10일 2쇄본 정오표 #

* 초판 1쇄를 구입하신 독자분들도 확인하시기 바랍니다 (전자책 ver2.0에는 모두 수정/반영된 사항입니다)

p60. 표 1-2 '2진수로 표현할 수 있는 값의 범위' 중

5행 '비트 개수' 20 항목의 '값의 범위' 오류

비트 개수 | 값의 개수 | 값의 범위

-----------------------------------------------

20 | 1,048,576 | 0 ... 1,048575

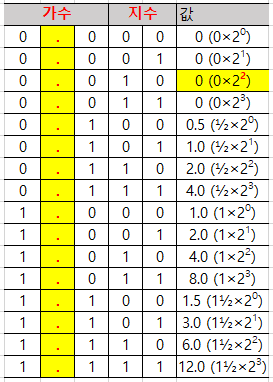

p70. 표 1-8 '부동소수점 2진수' 중에서

1) 가수부의 소수점(.) 위치 잘못되었습니다

2) 3번째 값 지수부 오타: 0*2^1 -> 0*2^2

p77. 표 1-10 '비트의 묶음을 부르는 이름'의 4째 줄 항목

32비트의 명칭을 수정합니다: 롱 워드(long word) -> 워드(word)

(표 바로 아래 "하드 워드, 롱 워드, 더블 워드라는 단어는 있는데 그냥 워드라는 단어를 쓰지 않는 이유가 궁금한 독자도 있을 것이다."라는 문장은 삭제합니다.)

p87. 2~3째 줄

감산 색 시스템은 흰색 광선에서 각 색의 파장을 제거하면서 색을 만들어내는 반면,

→

감산 색 시스템은 흰색 광선에서 각 색에 해당하지 않는 빛을 제거하면서 색을 만들어내는 반면,

p87. 밑에서 2째 줄

32비트(롱 워드) → 32비트(워드)

p89. 본문 4째 줄 (오타)

RBG로는 → RGB로는

p92. 하단 옮긴이 주석부 중 6~7째 줄

log(1.5×10^4×3×10^8) = log(1.5)×log(10^4)×log(3)×log(10^8) = log(1.5)×log(3)×4×8 = 32×log(4.5)임을

→

log(1.5×10^4×3×10^8) = log(1.5)+log(10^4)+log(3)+log(10^8) = log(1.5)+log(3)+4+8 = log(4.5)+12임을

p97. 3째 문단의 4째 줄 전기는 중력과 마찬가지로 → 전자기력은 중력과 마찬가지로

p127. 표 2-1 위 본문 마지막 세 줄 (본문 설명에 미흡한 부분이 있어, 본문을 수정합니다)

따라서 각 비트의 합을 계산하기 위해서는 (반)가산기가 2개 필요하다는 뜻이다. 세 입력 중 2개 이상이 1이면 올림이 발생한다. 표 2-1은 이렇게 올림까지 고려한 전가산기(full adder)의 진리표를 보여준다.

→

따라서 각 비트의 합을 계산하기 위해 반가산기를 2개 연결할 수도 있지만, 이보다 더 잘 할 수도 있다. 세 입력 중 2개 이상이 1일 때 올림이 발생한다. 표 2-1은 이를 고려한 전가산기(full-adder)의 진리표다.

p128. 첫 줄 (독자의 이해를 돕기 위해 본문을 수정합니다)

전가산기는 좀 더 만들기 복잡하고 그림 2-40처럼 생겼다.

→

이 표를 바탕으로 그림 2-40처럼 전가산기 회로를 구성하면 반가산기를 2개 사용할 때보다 시간 지연이 적은, 더 나은 회로를 만들 수 있다.

p131. '디멀티플렉서' 절의 첫 줄 (영문 병기 단어 철자 오류)

디먹스 dmux → demux

p151. '임의 접근 메모리' 절 본문 6째 줄 (영문 병기 단어 철자 오류)

커패시터 capicitor → capacitor

p171. 표 4-1 예제 ALU 명령코드 (5행(0100)과 6행(0101) '설명' 부분 4비트값 수정)

4비트값(범위는 0~16) → 4비트값(범위는 0~15)

p181. 표 4-2 (6행 ble와 8행 bge '설명' 부분 수정)

101 | ble | N(음수) 비트가 1이거나 Z(영) 비트가 1일 때 분기한다

111 | bge | N(음수) 비트가 0이거나 Z(영) 비트가 1일때 분기한다

p214. 본문 밑에서 3째 줄

열로 DRAM을 읽을 때 행으로 읽는 것보다 더 빠르다는 사실을 알 수 있다.

→ 행을 고정하고 열을 변화시키면서 DRAM을 읽을 때 더 빠르다는 사실을 알 수 있다.

p228. 본문 4~6행 (좀 더 명확한 설명을 위해 수정합니다.)

왜 그런지 궁금할 것이다. ~ 통과시킨다는 점에 유의하라.

→

'A 세그먼트가 1이고 B 세그먼트가 0이라면 이 두 세그먼트가 함께 켜지지 않나?' 같은 생각이 들었을지도 모르겠다. 그러나 LED의 'D'가 다이오드(diode: 전류를 한쪽으로만 흐르게 하는 소자)인 점을 기억한다면 그 생각이 틀렸음을 알 수 있다.

p237. 본문 3째 줄

미분 신호 방식 → 차동 신호 방식

p268. '래스터 그래픽' 절 밑에서 2째 줄

~ 레스터 방식이다. → 래스터 방식이다.

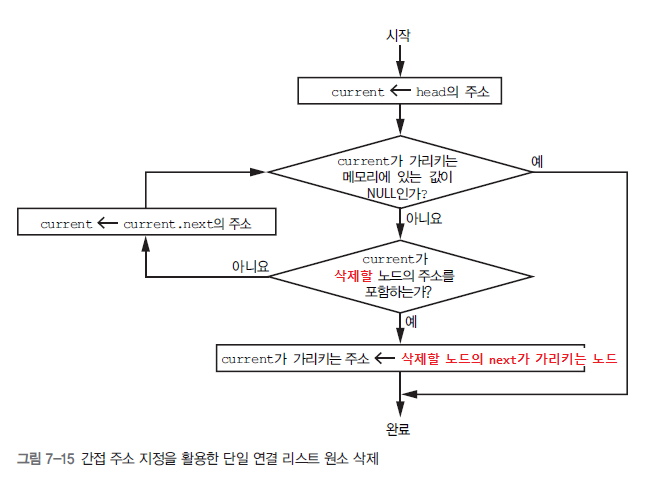

p286. 그림 7-15 (빨간 글씨 부분으로 수정)

삭제될 노드 → 삭제할 노드

delete.next가 가리키는 노드 → 삭제할 노드의 next가 가리키는 노드

p287. 5번 (아래에서 3은 원문 그대로 아래첨자입니다)

current3을 가리키는 → current3이 가리키는

p296. 본문 첫 줄

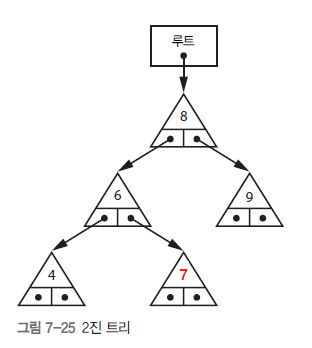

8, 6, 9, 4, 5를 삽입하면서 → 8, 6, 9, 4, 7을 삽입하면서

p296. 본문 마지막 줄

5도 비슷한 방식으로~ → 7도 비슷한 방식으로~

p297. 그림 7-25 (빨간 글씨 부분 수정: 5-> 7)

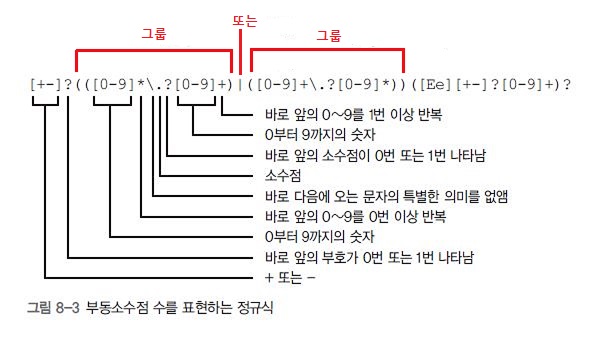

p328. 그림 8-3 ("그룹" "또는" 그룹"이 가리키는 위치 수정)

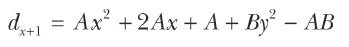

p424. 본문 내 3번째 수식: x제곱(x^2) 항의 계수 A가 빠졌습니다.

p443. 본문 밑에서 3째 줄

다음과 같은 삼각함수 동등성을 활용해 → 다음과 같은 삼각함수의 기본 공식을 활용해

p575. 본문 2~3째 줄

이로 인해 분명 DR-DOS보다 더 제값을 하는 제품이었던 DR-DOS는

→ 이로 인해 분명 MS-DOS보다 더 제값을 하는 제품이었던 DR-DOS는'

# 2021년 4월 8일 초판 1쇄본 정오표 # (상기 2쇄 정오표도 확인 바랍니다)

p42. 아래에서 9째 줄

기계적인 변환 적업으로 → 기계적인 변환 작업으로

p56. 참고 박스 2째 줄

두 비트에 대한 XOR 연산(a XOR b)은 (a OR b) AND (a AND b)와 같다.

→

두 비트에 대한 XOR 연산(a XOR b)은 (a OR b) AND (NOT(a AND b))와 같다.

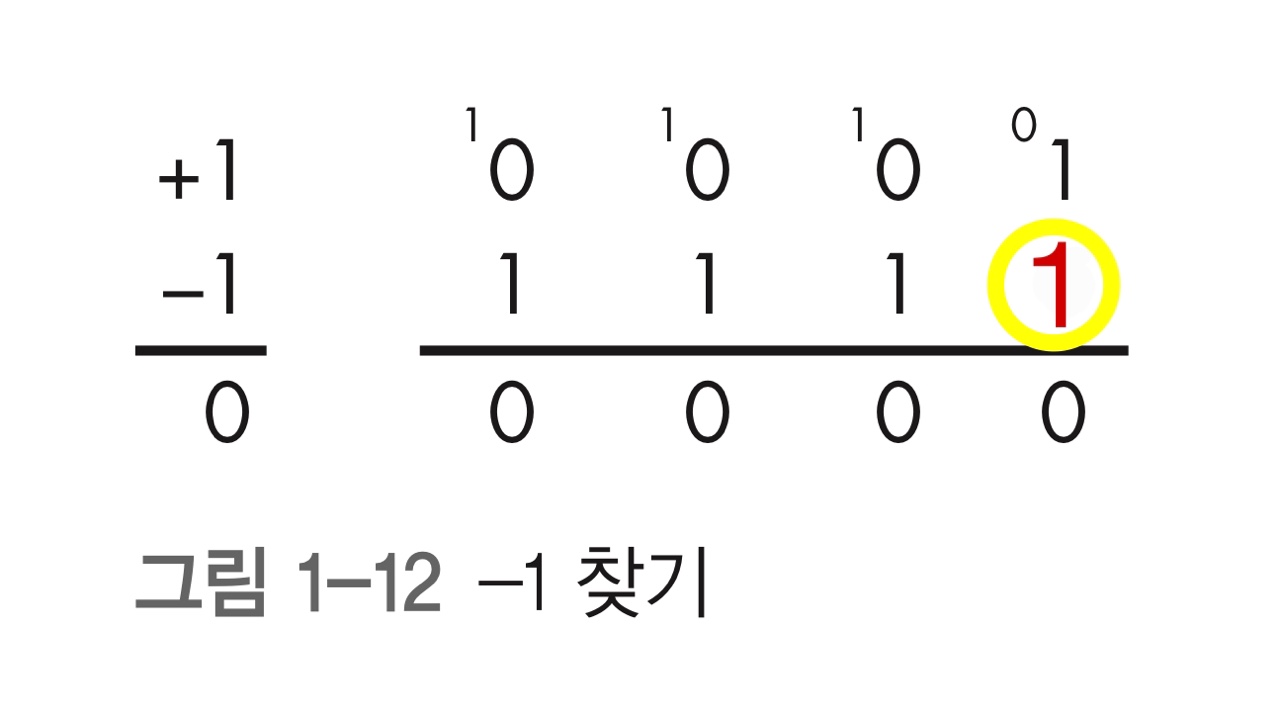

p66. 그림 1-12 수정

-1의 2의 보수이므로 1110이 아니라 1111로 수정합니다.

p87. 본문 5째 줄

가산 시스템이 가산 시스템보다 더 많은 색을 만들어낼 수 있다.

→

가산 시스템(빛 혼합)이 감산 시스템(물감혼합)보다 더 많은 색을 만들어낼 수 있다.

p104. 본문 밑에서 6째 줄 (영문 병기 단어 철자 오류)

저항 resistence → resistance

p113. '트랜지스터' 절 1째 줄 (영문 병기 단어 철자 오류)

트랜지스터 transister → transistor

p124. 하단 주석 14번 마지막 줄 (영문 병기 단어 철자 오류)

하이 임피던스 high impedence → high impedance

'+ 도서 오류 정보' 카테고리의 다른 글

| [정오표] 엘라스틱 스택 개발부터 운영까지 (2) | 2021.08.24 |

|---|---|

| [정오표] 스프링 부트 실전 활용 마스터 (0) | 2021.06.10 |

| [정오표] 핵심 딥러닝 입문: RNN, LSTM, GRU, VAE, GAN 구현 (0) | 2021.01.28 |

| [정오표] 구글 빅쿼리 완벽 가이드 (0) | 2020.11.20 |

| [정오표] 파이썬 알고리즘 인터뷰 (21) | 2020.07.21 |

댓글